# **XRC Co-simulation Library v1.5**

Copyright © 2004 Alpha Data Parallel Systems Ltd. All rights reserved.

This publication is protected by Copyright Law, with all rights reserved. No part of this publication may be reproduced, in any shape or form, without prior written consent from Alpha Data Parallel Systems Limited.

Alpha Data Parallel Systems Ltd. 4 West Silvermills Lane Edinburgh EH3 5BD Scotland UK

Phone: +44 (0) 131 558 2600 Fax: +44 (0) 131 558 2700 Email: support@alpha-data.com

## 1 Introduction

The Alpha Data XRC Co-simulation Library is a Simulink Blockset designed for use in conjunction with Xilinx System Generator 6.3 and Matlab Release 14.1. This blockset enables System Generator Models to be Co-simulated using Alpha Data ADM-XRC-II-L, ADM-XRC-II, ADM-XRC-II-Pro-Lite (ADM-XPL), ADM-XRC-II-Pro (ADM-XP), ADP-DRC-II and ADP-WRC-II FPGA reconfigurable computing cards. The System Generator design methodology incorporating Co-simulation allows a very rapid move from Simulation in Simulink to Verification on Hardware. This design methodology can be used incrementally, with Co-simulated Hardware in the Loop modules used to accelerate the development and simulation of larger designs.

#### 2 Installation Instructions

The XRC Co-simulation Library is provided as a zip file and a Matlab installation script:

xrc\_cosim\_blockset.zip setup\_cosim.m

1) Open Matlab

2) Change Directory to where xrc\_cosim\_blockset.zip and setup\_cosim.m have been downloaded.

3) Type setup\_cosim

4) Quit Matlab

### 3 Using The Library

Once installed, board options for the ADM-XRC-II, ADM-XRC-II-Lite, ADM-XRC-II-Pro-Lite, ADP-DRC-II, ADP-WRC-II will appear in the Compilation->Hardware In The Loop menu of the System Generator GUI (accessed by double clicking on the System Generator token in your design). You can select the correct Alpha Data board and the correct FPGA specification form this GUI.

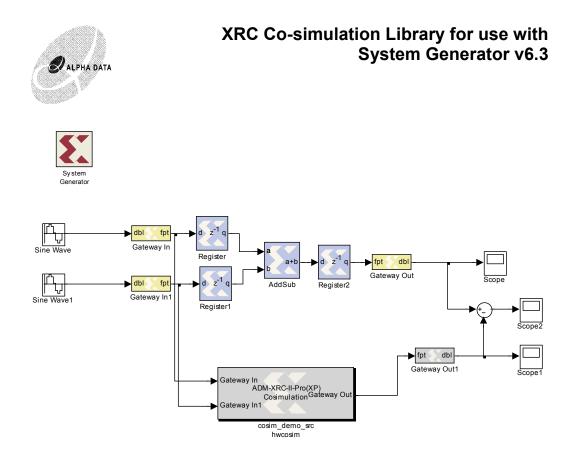

Now when Generate is pressed in the System Generator GUI, the VHDL is still created as normal, but afterwards, the Xilinx (and possibly 3rd party) synthesis tools are run to create a bitstream for the device and board selected. After this is finished, a new library containing a hardware cosimulation block will appear, as shown in figure 2.

| > data<br>Alpha Data XRC<br>Cosimulation sum ><br>> load_coeffs |  |

|-----------------------------------------------------------------|--|

| imageproc_hwcosim                                               |  |

|                                                                 |  |

|                                                                 |  |

Figure 1: Hardware Cosimulation Block

This block can be inserted into a System Generator Simulink design in place of the model synthesized, for testing and verification or even as a simulation component, to accelerate the simulation of a higher level design. The block has 3 parameters, specifying the clock period, the generated bitstream and which Alpha Data board (if multiple boards are installed in the system) to use.

#### 4 Example Files

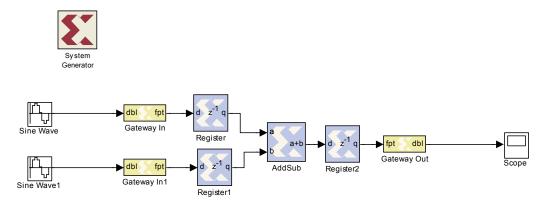

A simple example for demonstrating how to use the cosim blockset is provided in cosim\_demo\_src.mdl. This example adds two sine waves together, and displays the outputs on a scope.

A second model cosim\_demo.mdl is provided to show how to insert the Hardware in the Loop block into a simulation, and compare the results:

Note that the conversion between doubles and Fixed Point data types is handled using the Gateway blocks. The cosimulation block can accept doubles as inputs, but this may cause slight mismatches between Simulation and hardware in the loop results.